- cross-posted to:

- [email protected]

- cross-posted to:

- [email protected]

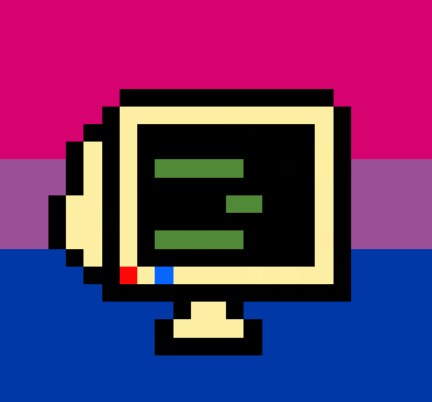

Javascript should say “you are a masochist and a nerd”

Who thought of that and how have they managed to sustain their core bodily functions this long?

Probably this guy

with his therapist 🤣

I take it that he dictated the book to his therapist from a state of paralysis.

That should be a dog fucking a football.

Rust: you are a nerd wearing programming socks.

Trying to rewrite everything in the universe

It’s a shame that the Rust rewrite of the GNU coreutils was named uutils and not uwutils.

I am not in this chart because my favourite programming languages are too nerdy for the cool programming nerds to include in their nerd chart.

Therefore I can conclude I am not a nerd

I don’t think that’s how it works.

Same here.

VHDL represent. Although it’s arguably not a “programming language”

you get out of here with your hardware descriptions!

I see your VHDL, and raise with Prolog… or Postscript, similar paradigm.

You work at IBM or something? Who even still uses VHDL?

A ton of people. Anything aerospace, DoD, Space, or critical infrastructure. All those industries have to use VHDL to support legacy products from the 80s and 90s. At that point everyone is like, “Sure its 2025, by why switch to SystemVerilog? We already know VHDL.” and thus you got a whole army of engineers making next gen satellites, augmented reality headsets, etc. …… in VHDL 93.

Is it such a hassle learning verilog if you know vhdl or vice versa?

Not really, HDL is HDL. At the end of the day, as long as you know what you want to do electrically then everything else is an exercise of translating that desire into VHDL, Verilog, or SystemVerilog. The only real hassle is creating test-benches and verification simulations. But at that point it’s discretionary towards the designer. A lot of tools coming from Intel, Xilinx, and Synopsys allow you to “black box” components. So a module written in VHDL can be incorporated into a design or test bench written in verilog and vis-versa. IMHO VHDL is still dominant because grey beard chief engineers throw a little hissy fit at design reviews when they learn the junior engineers did everything in verilog.

Tbf, I am not a grey beard chief engineer, and I strongly prefer VHDL for design. For verification I actually really like SystemVerilog.

VHDL is strongly types, which prevents a lot of issues with types that I’ve hit with [System]Verilog.

Also, having learned VHDL first, I think it is easier to go from VHDL to Verilog, as opposed to vice versa. And this is mainly because VHDL is stricter.

Lol, so much of the FPGA industry 🤣. Especially East coast of the US

I do mostly c/c++ for an embedded product, but one of the modules in the system uses an FPGA programmed w/ VHDL. So I’ve gotten to do a few deep dives into that code in the past couple years.

It’s been decades since I’ve had to write new VHDL or Verilog though.

Super nerd

Turbo Nerd

Nerd.

Fair.

Cobol: you are old, and a nerd, and probably making some sweet cheddar right now propping up a mid to late 20th century beast somewhere.

Assembly: you are a cyborg.

Assembly: you are a cyborg.

Or programming a tiny microcontroller to blink a led as efficient as possible.

Something wrong with:

#include <Arduino.h> void loop() { digitalWrite(13, HIGH); delay(1000); digitalWrite(13, LOW); delay(1000); }? 😂🤮

Obviously the only correct way to blink an LED is to use a hardware timer to trigger a DMA transfer which stores a bit in the pin toggle register at a set interval

yeah! Or or use the interrupt pins and a 555 timer! both options are better than python though at least.

I know who made this included React and HTML specifically to trigger us programmers, to that I say… well played >:(

TIL fortran has a logo

Where would COBOL fall?

“You’re in a Nursing Home”

“and nerd”

The revenge!

Lisp gang rise up! uses inhaler

As a haskell nerd, I feel that I have the moral authority to declare you king of the nerds.

“Ha! You think your language has macros? You call that a macro?! This list processing code is a list of tokens, why wouldn’t it be able to edit itself?”

It breaks my brain.

When they said, “Don’t write self modifying code”, they obviously didn’t mean me! /s

Is haskell still alive?

Absolutely. It’s just that less fuss is being made about it on hacker news because the cool kids say you’ll be a better programmer in other languages if you learn rust when they used to say that you’ll be a better programmer in other languages if you learn haskell.

With stack (consistent package version snapshot database based project starter and build tool) instead of cabal, you get the transferable and repeatable build benefits of docker with none of the hassle. Just

stack newat the start andstack buildorstack replduring development. Nothing gets bitrotten any more.Nah, I am not talking about hackernews buzz. I just thought it is dying couple of years ago.

I’ve addressed both popularity (waned - rust is the cool new difficult-to-learn principled language now) and bitrottenness (rock solid). I’m not sure what else you were meaning if it wasn’t either of these.

Nah, too relevant, what with LUA, functional programming, currying, and AI, et. al. ;)

I did an AI robot arena bot in college using Lisp. That was interesting.

R

We can reject the null hypothesis that you are not a nerd at significance $\alpha < 0.001$.

oh wait, shit let me run that again, my data frame is full of NA somehow, again.

Aww I guess i’m fine since i mainly write in BBC BASIC SDL lol

Have you come to 2025 in a time machine? Can I borrow it?

Sorry I’m using it at the moment doing research for a Roman trading game I’m writing in BASIC.

deleted by creator

Neeerd

how dare you Im not an engineer

What language is that engineer and a nerd one?

Matlab.

Where holyC

You are a christian nerd

What is the bottom right language?

Perl. It was the cool thing from 1998 to 2008.

Still the linux sysadmin’s language of choice!

what about BASIC